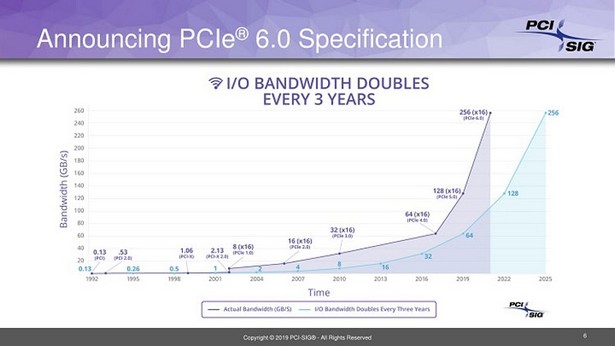

Стали известны подробности работы PCIe 5.0 и PCIe 6.0, которые ожидаются на рынке уже в следующие пару лет

20.06.19

Согласно устоявшейся традиции, каждая новая версия интерфейса PCI Express должна была раз в 3 года. Работы над шиной PCIe 4.0 задержались на семь лет. Но выход чистовых спецификаций PCIe 5.0 и PCIe 6.0 должны исправить это положение и уже известны некоторые технические данные по ним. PCIe 6.0 ожидают на рынке уже в 2021 году.

Переход к новой версии снова в 2 раза увеличит скорость передачи данных: теперь с 32 гигатранзакций в секунду до 64 гигатранзакций в секунду (в пересчёте на 8 линий).

Для достижения улучшенных показателей разработчики изменят сигнальную структуру интерфейса. Так, вместо передачи последовательности импульсов без возврата к нулю (NRZ, no-return-to-zero) будет реализована схема передачи с амплитудно-импульсной модуляцией (PAM4). ![]() На практике вместо последовательности 0 и 1 будет использоваться градация сигнала с четырьмя уровнями. Это увеличит плотность передачи данных и ёмкость канала, но это также чревато увеличением задержек.

На практике вместо последовательности 0 и 1 будет использоваться градация сигнала с четырьмя уровнями. Это увеличит плотность передачи данных и ёмкость канала, но это также чревато увеличением задержек.

В PCI Special Interest Group (SIG) пока не определились с уровнем задержек в стандарте PCIe 6.0. По мнению специалистов, латентность составит до десятков наносекунд, как у памяти типа DRAM. Основной вклад в рост задержек принесёт новый способ коррекции ошибок. Технология PAM4 требует перейти на прямое исправление ошибок за счёт избыточности или FEC (requires forward error correction). Обе эти технологии отсутствуют в спецификациях PCIe 5.0.

Другим важным моментом перехода на PCIe 6.0 станет удорожание комплектующих и материалов для плат. С ростом скорости передачи данных эффективная дальность линий снижается. Чтобы компенсировать это, нужны материалы, снижающие взаимные помехи сигналов от разных линий и различные волновые эффекты в линиях. Такое сырьё есть и оно уже используется в решениях для передачи данных по медным кабелям на скоростях свыше 200 Гбит/с. Что касается схемотехники, то с ростом скорости нужно вводить такие элементы как ретаймеры. Это чипы, которые восстанавливают целостность синхроимпульсов в условиях помех или слабого сигнала. Например, дальность передачи сигнала по спецификациям PCIe 4.0 составляет около 30 см без использования разъёмов. Спецификации PCIe 6.0 без специальных решений не смогут передать информацию даже на эту дистанцию.

One thought on “Стали известны подробности работы PCIe 5.0 и PCIe 6.0, которые ожидаются на рынке уже в следующие пару лет”

Добавить комментарий

вологість:

тиск:

вітер:

Обзор планшета Oppo Pad Neo: перспектива

Планшет Oppo Pad Neo является представителем среднего-высокого класса. У него большой экран, емкая батарея и достаточная производительность. Насколько он универсален, попробуем разобраться

HMD анонсировала обновленные модели телефонов Nokia 6310, 5310 и 230

HMD Nokia телефонЦены на эти телефоны HMD пока не объявлены. Важно отметить, что все три Nokia 6310, 5310 и 230 поддерживают только сети 2G, поэтому они не будут работать в сетях 3G или более новых.

Опрос: 53 % пользователей Viber стали гораздо меньше читать новости в 2023 году, а 31% читают так же

Viber исследования10% пользователей вайбер вообще никогда не следили за новостями, тогда как 31% читают так же, и еще 6% — даже чаще.

Что-то, судя по тому что написано в последних абзацах, PCIe 6.0 выглядит как набор костылей… увеличение скорости это конечно хорошо, но вот все эти сопутствующие проблемы и пути их решения пока не внушают энтузиазма